Comprensione della potenza del fermo S-R: un gateway per l'elettronica moderna

I bloccanti sono semplici dispositivi digitali che archiviano un po 'di informazioni e mantengono quel valore fino a quando non ottiene nuovi segnali di input.Sono utilizzati nei sistemi digitali per contenere temporaneamente dati binari.I chiavistei possono essere realizzati utilizzando diversi tipi di porte logiche di base come e, o, non, NAND e né porte.Questo articolo esplora la progettazione, la funzione, le variazioni e gli usi del fermo S-R, sottolineando il suo miglior ruolo nella moderna elettronica e il suo utilizzo nei circuiti pratici e nelle simulazioni della logica digitale.

Catalogare

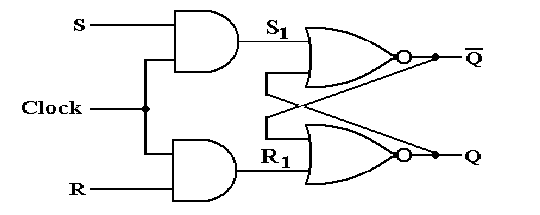

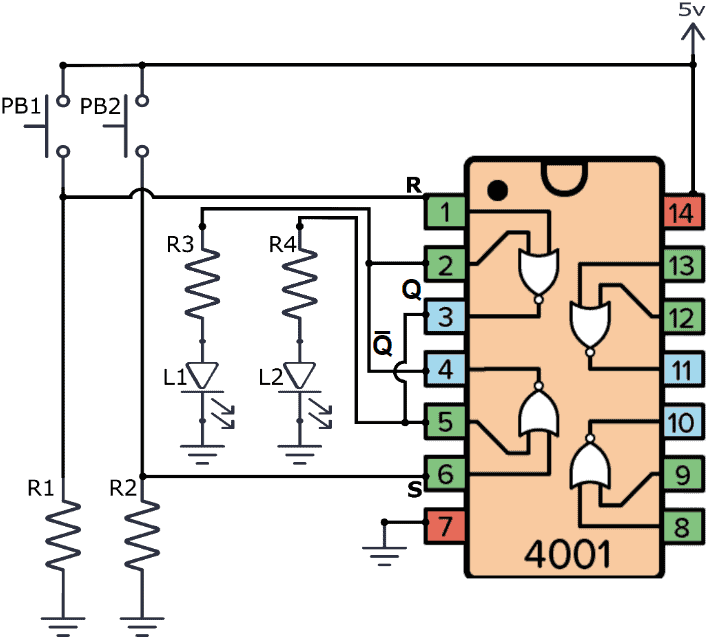

Figura 1: diagramma del circuito a chiusura S-R

Struttura del fermo S-R

Il fermo S-R (set-reset), una pietra miliare dell'elettronica digitale, è un multivibratore bistabile.È in grado di mantenere uno dei due stati distinti e stabili indefinitamente senza input esterni.Questa funzionalità rende il blocco SR un componente principale nell'archiviazione della memoria e nelle operazioni di commutazione su diversi dispositivi elettronici.

Strutturalmente, il fermo SR è costituito da due porte interconnesse né organizzate in una progettazione del ciclo di feedback.Questa disposizione specifica è importante poiché offre i prerequisiti per la bistabilità.L'output di ciascuna né del gate è collegata direttamente all'ingresso dell'altro, creando un ciclo continuo di feedback che sostiene il funzionamento del fermo.

Figura 2: fermo S-R e segnale di clock (CLK)

Espandendo il design di base, il chiusura SR gated introduce un input aggiuntivo: il segnale di clock (CLK).Questo potenziamento incorpora un input di clock che porta il livello di controllo, integrando le operazioni di chiusura in sistemi che richiedono la sincronizzazione.Questa sincronizzazione obbligata in quanto determina i momenti precisi in cui il fermo può cambiare gli stati, appropriatamente descritti dal termine "gated".L'inclusione del segnale di clock garantisce che le modifiche allo stato di uscita del fermo si verificano solo durante la fase di clock attiva, in genere sul bordo di salita o in calo del segnale CLK.

L'introduzione dell'input CLK non solo preserva le proprietà del fermo SR di base, ma allinea anche il suo funzionamento con le dinamiche temporali di sistemi digitali più grandi.Questo desiderio di allineamento di mantenere l'integrità dei dati e garantire che le transizioni di stato si verifichino senza problemi o modifiche non intenzionali, in particolare in configurazioni di circuiti complessi in cui possono interagire più chiusure.Controllando quando il cuscinetto risponde ai comandi SET e RESET, il sistema può evitare problemi come le condizioni di gara e altri errori legati alla tempistica che potrebbero altrimenti interrompere la stabilità e le prestazioni del sistema.

Stati operativi del fermo S-R

Il suo funzionamento dipende dagli ingressi di due segnali di controllo: set (s) e reset (R).Qui, spieghiamo come questi input influenzano gli output e gli stati del fermo SR.

Caso 1: set condizione

Quando l'ingresso set (s) è elevato (1) e l'ingresso di reset (R) è basso (0), il cuscinetto inserisce la condizione set.In questo stato, il gate NAND collegato all'ingresso R emergerà un segnale basso a causa dell'ingresso elevato da S. Questo segnale basso fa sì che il secondo gate NAND produca un segnale elevato, impostando da Q su alto (1) e Q-bara basso (0).Questo stato è stabile e manterrà Q elevato fino a quando gli input non cambiano, mostrando la capacità del fermo di archiviare uno stato elevato.

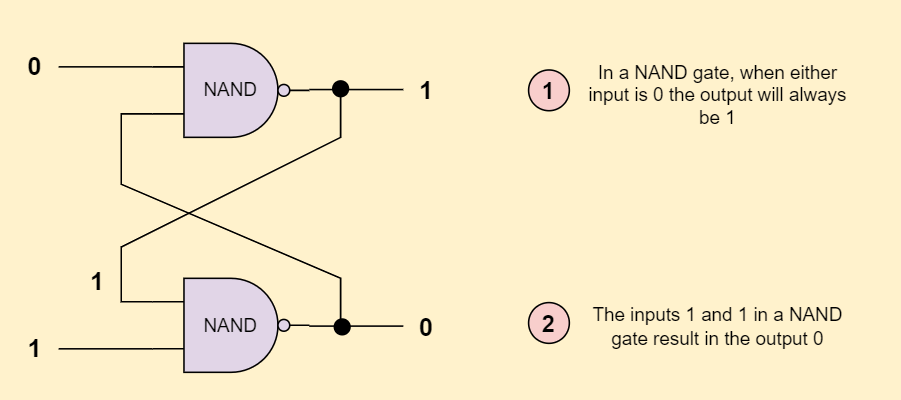

Figura 3: lo stato del set

Caso 2: condizione di ripristino

Quando S è basso (0) e R è alto (1), il fermo inserisce la condizione di ripristino.Qui, l'alto input su R e l'ingresso basso su S rendono il gate NAND collegato all'uscita R un segnale basso.Questo segnale basso imposta Q su basso (0) e Q-bar su alto (1), ripristinando efficacemente il fermo.Ciò dimostra la capacità del chiavistello di tornare a uno stato basso stabile in Q quando vengono dati gli input giusti.

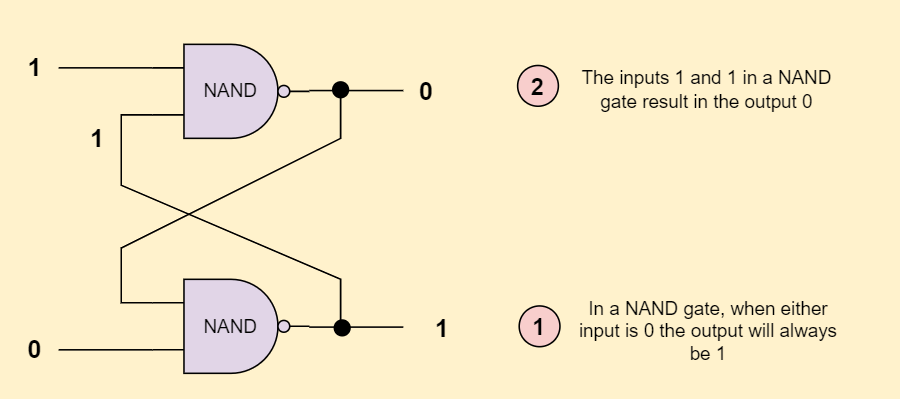

Figura 4: lo stato di ripristino

Caso 3: stato non valido

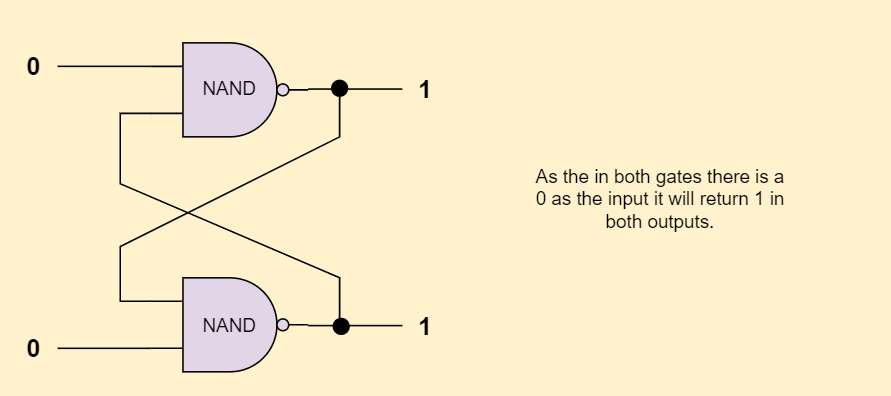

Se sia S e R che sono bassi (0), entrambi gli ingressi per le porte NAND sono bassi, causando alti entrambi gli output Q e Q-Bar.Questo stato è chiamato non valido o proibito perché infrange la regola di base secondo cui Q e Q-bar dovrebbero essere sempre opposti.Questo scenario evidenzia la limitazione del fermo SR, sottolineando l'importanza di evitare tali stati instabili attraverso una corretta gestione dell'input.

Figura 5: lo stato non valido

Caso 4: Tenere Condizioni

Quando entrambi gli ingressi sono alti (1), le uscite dipendono dallo stato precedente del fermo anziché dagli ingressi correnti.Questa è nota come condizione di attesa, in cui Q e Q-bar rimangono invariati, preservando l'ultimo stato valido del chiavistello.Per alcune applicazioni, è importante essere in grado di mantenere lo stato bloccato per lunghi periodi di tempo senza modifiche, come le celle di archiviazione della memoria in cui l'integrità dei dati è di grande importanza.

Figura 6: lo stato di attesa

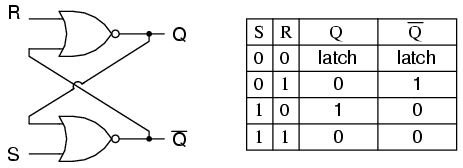

Cliet S-R con una tabella della verità

Questo tavolo non è solo uno strumento teorico, ma è anche pratico sia per i circuiti che per gli studenti.Li aiuta a vedere come si comporta il fermo in molte condizioni.Di seguito, presentiamo la tabella di verità completa per il fermo SR, seguita da spiegazioni e approfondimenti pratici per ogni condizione.

|

S |

R |

Q |

Q-bar |

STATO |

|

0 |

0 |

1 |

1 |

Non valido |

|

0 |

1 |

0 |

1 |

Reset |

|

1 |

0 |

1 |

0 |

Impostato |

|

1 |

1 |

Q |

Q-bar |

Presa |

Grafico 1: SR

Tavolo della verità di chiusura

Spiegazione di ogni riga

Imposta condizione (s = 1, r = 0): questa riga mostra che quando s è alto e r è basso, Q è impostato su alto (1) e Q-bar a basso (0).Ciò rispecchia la risposta del circuito a un comando set, memorizzando efficacemente un "1".

Condizione di ripristino (s = 0, r = 1): qui, gli ingressi indicano un'operazione di ripristino.Di conseguenza, Q viene ripristinato a basso (0) e Q-bar è impostato su alto (1).Questo stato dimostra la capacità del fermo di tornare a uno "0".

Condizione non valida (s = 0, r = 0): entrambe le uscite diventano elevate in questa condizione, il che è generalmente evitato perché si traduce in entrambe le uscite sono identiche.Ciò può portare a instabilità o comportamento indefinito nel fermo, poiché viola la regola secondo cui Q e Q-bar dovrebbero essere sempre opposti.

Tenere la condizione (s = 1, r = 1): in questo scenario, il fermo mantiene il suo stato precedente, mettendo in mostra la sua capacità di trattenere l'ultimo stato set a meno che non abbia esplicitamente comandato di cambiare.

Approfondimenti e suggerimenti pratici

Comprensione degli output: ricorda sempre che Q e Q-Bar sono idealmente completati.Qualsiasi deviazione da questa regola (come mostrato nella condizione non valida) indica un problema o un'errore di configurazione.

Evitare lo stato non valido: è indispensabile che i progettisti si prendano cura di prevenire la situazione in cui S e R sono entrambi bassi.L'implementazione di logiche o interblocchi aggiuntivi può aiutare a prevenire questo stato.

Utilizzando la condizione di sospensione: la condizione di mantenimento può essere particolarmente conveniente nelle applicazioni che richiedono la conservazione dei dati nel tempo.La manutenzione dell'integrità dei dati può dipendere dall'assicurare che il fermo non si inserisca inavvertitamente nello stato set o di ripristino.

Interpretazione della tabella della verità: quando si progettano o debug di circuiti, fare riferimento alla tabella della verità per prevedere in che modo i cambiamenti nell'input influenzeranno l'output, specialmente in circuiti complessi in cui vengono utilizzati più chiavistelli.

Dinamica funzionale del fermo S-R

Il fermo S-R (set-Reset) funziona bene solo se i suoi input sono gestiti correttamente.Per capire come funziona, è necessario sapere in che modo diverse combinazioni di input influenzano gli output, Q e Q-bar (l'opposto di Q).

Figura 7: fermo S-R

Se entrambi i set (S) e il reset (R) vengono attivati contemporaneamente (S = 1 e R = 1), il fermo va in uno "stato proibito", in cui entrambe le uscite, Q e Q-bar, sono 0.Questo è un problema perché normalmente, Q e Q-bar dovrebbero essere opposti.

In condizioni normali, per impostare il fermo, si attiva S (set S su 1) e disattivato R (set R su 0).Questo fa andare in alto Q (1) e Q-BAR (0), mostrando che il fermo può archiviare un 1. Per ripristinare il fermo, si attiva R (set R a 1) e disattivato S (set S su 0).Questo fa diventare Q basso (0) e Q-bar (1), mostrando che il fermo può cancellarsi e archiviare uno 0.

Quando entrambi gli input sono disattivati (S = 0 e R = 0), il latch mantiene il suo ultimo stato, set o reset.Questo è utile per archiviare i dati o mantenere uno stato senza bisogno di input continui.

Le condizioni di gara possono complicare il funzionamento del fermo S-R.Questi errori si verificano quando gli output si basano fortemente sui tempi delle modifiche di input, portando a risultati imprevedibili se gli input cambiano quasi allo stesso tempo.Per prevenire questo e garantire che il fermo funzioni in modo affidabile, vengono spesso utilizzati meccanismi di delay di tempo.Questi ritardi assicurano che un input si attivi dopo che l'altro ha avuto il tempo di stabilizzarsi.Affinché il chiavistello sia utilizzato nei circuiti digitali in cui è richiesto un tempismo preciso, deve funzionare in modo coerente e mantenere uscite costanti.Ciò è reso possibile dai tempi controllati.

Diagramma logico del fermo S-R

Il latch SR è un circuito logico sequenziale di base con due configurazioni principali: né nand Gates.Ogni configurazione influisce su come funziona il latch e risponde agli input, consentendo la personalizzazione per diverse applicazioni elettroniche.

Figura 8: il diagramma logico rappresenta il fermo S-R usando NAND GATE

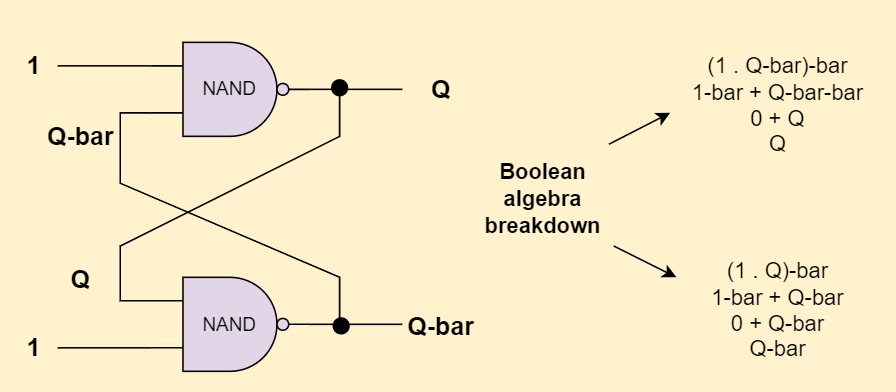

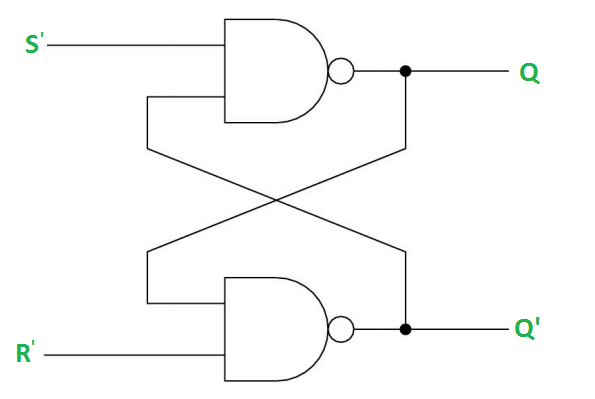

Implementazione usando Nand Gates

Quando si costruisce un fermo SR con Nand Gates, viene utilizzato un circuito di feedback per mantenere il suo stato.Questa configurazione consente al fermo di mantenere il suo stato precedente quando entrambi gli input (S e R) sono bassi.Nand Gates Output Alto a meno che entrambi gli ingressi non siano alti.Lo stato del fermo cambia quando un input è alto e l'altro è basso.È meglio evitare di impostare sia S che R alti contemporaneamente perché questo costringe entrambe le uscite per abbassare, portando a uno stato indefinito in cui le uscite non sono più complementari.Una corretta gestione dell'input è un must per prevenire l'instabilità nei fermo SR a base di NAND.

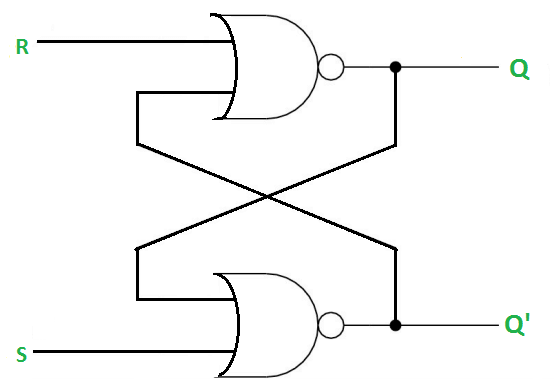

Implementazione usando né Gates

L'uso di né cancelli per un latch SR cambia le condizioni operative rispetto alle porte NAND.In questa configurazione, il fermo contiene il suo stato quando entrambi gli ingressi sono elevati.Il chiusura del fermo lo stato quando un input è basso e l'altro è alto.Né porte output in alto solo se entrambi gli ingressi sono bassi.Questa configurazione è utile nei circuiti in cui lo stato predefinito deve avere entrambe le uscite basse, garantendo un'uscita prevedibile in condizioni ad alto livello.Tuttavia, è meglio evitare di fissare entrambi gli input allo stesso tempo, poiché ciò causa output contrastanti e riduce l'affidabilità del fermo.

Figura 9: il diagramma logico rappresenta il fermo S-R usando il gate NOR

Circuito di esempio

Esplorare come funzionano i chiusure SR nella vita reale mostra la loro utilità.Un buon esempio è un circuito che utilizza il chip CD4001, che ha quattro né porte.Questo circuito mostra come i cuscinetti SR possono controllare dispositivi come LED con semplici azioni come la pressione dei pulsanti.

In questo esempio, le porte NOR nel chip CD4001 sono impostate per creare un fermo SR.Due porte sono collegate in un circuito di feedback per mantenere lo stato di fermo.I pulsanti vengono aggiunti al circuito come ingressi per il set e il ripristino.Premendo un pulsante modifica lo stato dell'input, che modifica il fermo e lo stato a LED.Ad esempio, premendo il pulsante Imposta illumina il LED e rimane acceso anche dopo il rilascio del pulsante, mostrando come il fermo può mantenere uno stato.

Per migliorare il circuito, è possibile aggiungere più LED per mostrare lo stato di uscita di Q e Q-BAR.Questo rende più facile vedere come funziona il fermo, il che è molto utile per gli ambienti di apprendimento.

Figura 10: Clietta S-R usando il chip CD4001

Implementazione del codice

La traduzione della logica operativa di un latch SR nel software mostra come la progettazione della logica digitale può funzionare sia nell'hardware che nelle simulazioni virtuali.L'uso di un linguaggio di programmazione come C ++ è efficace perché supporta la logica e il controllo complessi necessari per imitare i comportamenti hardware.

Per creare un latch SR in C ++, inizi definendo le porte della logica di base come funzioni che agiscono come le loro versioni hardware.Ad esempio, una funzione NAND GATE restituirebbe l'opposto dell'operazione e sui suoi input.Allo stesso modo, una funzione NOR GATE restituirebbe l'opposto dell'operazione o.Con queste funzioni di base, è possibile modellare il comportamento del latch SR creando un ciclo di feedback tra queste funzioni di gate, in base al diagramma del circuito del latch.

Il codice avrebbe in genere un ciclo che controlla continuamente gli stati degli ingressi (set e reset) e aggiorna di conseguenza gli output (Q e Q-BAR).Le dichiarazioni condizionali all'interno di questo ciclo determinano in che modo i cambiamenti nell'input influiscono sulle uscite, imitando da vicino il comportamento fisico del fermo SR.Ad esempio, se entrambi gli ingressi impostati e reset sono bassi, le uscite rimangono le stesse.Se il set è elevato e il ripristino è basso, l'output Q diventa elevato e la Q-bar diventa bassa, replicando la condizione di impostazione del fermo.

Ecco un semplice esempio di come potrebbe apparire nel codice:

Figura 11: SR LATCH in C ++

Questo codice imposta un semplice fermo SR utilizzando né Gates e controlla e aggiorna continuamente lo stato di chiusura in base agli input.

Applicazioni del fermo SR

Sistemi di controllo nelle operazioni motorie: il fermo SR richiesto dai sistemi per il controllo del motore.Utilizzando gli interruttori a pulsante di start (s) e stop (R), il latch SR mantiene in funzione un motore anche dopo il rilascio del pulsante di avvio.Questa configurazione garantisce che il motore funziona continuamente fino a quando non si è fermato, migliorando la sicurezza e la convenienza.

Archiviazione di memoria e dati: quando si crea circuiti di memoria più grandi, il latch SR svolge un ruolo poiché può archiviare un singolo bit di dati.Mantiene i dati in uno stato stabile fino all'aggiornamento, formando la base delle celle di memoria nel calcolo digitale.

Controllo e gestione del segnale: nelle applicazioni del segnale di controllo, i chiusure SR contengono bit specifici fino a quando non vengono soddisfatte determinate condizioni, garantendo una sequenza e un tempismo adeguati nelle operazioni.La precisione nell'elaborazione del segnale e nel flusso di dati dipende da questo.

Circuiti di debouncing: i chiusure SR stabilizzano i segnali da interruttori e pulsanti meccanici, prevenendo falsi innesco e errori causati dal "rimbalzo" quando vengono premuti gli interruttori.Ciò è particolarmente adatto alle interfacce digitali come le tastiere.

Elementi di base nei sistemi digitali: la progettazione di infradito e contatori, che sono adatti per i tempi e il sequenziamento in elettronica, si basa fortemente sui fermo SR.Sono anche usati come chiavistelli a impulsi per attivi a stato rapido.

Applicazioni specializzate: nei sistemi asincroni, le variazioni come il latch D vengono utilizzate per un trasferimento di dati sicuro e affidabile.Nei sistemi a due fasi sincroni, i bloccanti dei dati riducono il conteggio dei transiti, migliorando l'efficienza e riducendo i ritardi.

Implicazioni più ampie nell'elettronica: i chiusure SR sono ampiamente utilizzati nei circuiti di gating di alimentazione, giocando un ruolo nella conservazione dell'energia all'interno dei dispositivi elettronici.Gestiscono gli stati di potenza a un livello dettagliato, contribuendo all'efficienza energetica complessiva dei sistemi digitali.

Conclusione

Il fermo S-R mostra l'importanza di semplici strutture logiche in sistemi digitali complessi.Osservando le sue diverse configurazioni e il modo in cui funziona, vediamo che il fermo S-R mantiene i dati stabili e rende i sistemi efficienti e affidabili.Può funzionare in varie condizioni, mostrato da tabelle di verità e diagrammi logici, rendendolo adattabile per diversi usi, dal controllo del motore ai circuiti digitali di base come infradito e contatori.Il fermo S-R è adatto in molte applicazioni pratiche, come le celle di memoria nei computer e i circuiti di debuncing nelle interfacce digitali, migliorando l'efficienza e riducendo gli errori nei dispositivi elettronici.Con meccanismi di feedback e un'attenta gestione del segnale di ingresso, il fermo S-R è utile per progettare sistemi digitali più affidabili ed efficienti.Studiare la sua funzione attraverso simulazioni software aiuta a collegare l'elettronica teorica con applicazioni del mondo reale, rendendo il fermo S-R un argomento importante per gli ingegneri elettronici nuovi ed esperti.

Domande frequenti [FAQ]

1. Qual è lo scopo del fermo SR?

Il fermo SR viene utilizzato per archiviare un singolo bit di dati;È una forma base di memoria nei circuiti digitali.La sua funzione principale è quella di conservare un po 'lo stato fino a quando non viene modificato dai segnali di input.

2. SR è attivo il latch in alto o basso?

Il fermo SR è in genere alto attivo, il che significa che risponde agli input elevati (livello logico 1).Quando gli ingressi S (set) e R (reset) sono elevati, attivano le modifiche nell'output.

3. Qual è lo svantaggio con un fermo SR?

Un grande svantaggio del fermo SR è la sua suscettibilità a una condizione non valida in cui entrambi gli ingressi set e di ripristino sono elevati contemporaneamente.Questa situazione porta a un output non definito, che può comportare un comportamento inaffidabile o imprevedibile.

4. Quali sono le regole per il fermo SR?

Se S (set) è alto e R (reset) è basso, l'uscita Q è impostata su alto.

Se R è alto e S è basso, l'output Q viene ripristinato a basso.

Se entrambi S e R sono bassi, l'output mantiene il suo stato precedente.

Se entrambi S e R sono alti, l'output è indefinita o non valida.

5. Che cos'è la memoria nel latch SR?

La memoria in un latch SR si riferisce alla sua capacità di mantenere indefinitamente lo stato di output (in alto o basso), fino a quando non riceve input per cambiare lo stato.Questo lo rende un dispositivo bistabile, ideale per una semplice memoria di memoria.

6. Quali sono le uscite del fermo SR?

Il fermo SR ha due uscite, Q e Q '(Q-BAR).Q rappresenta lo stato corrente, mentre Q 'è l'inverso di Q. Quando Q è alto, Q' è basso e viceversa.

7. Dove usiamo latch?

Quando sono richiesti l'archiviazione dei dati a breve termine o la conservazione statale, i chiusure vengono impiegati in diversi tipi di applicazioni.Ciò include l'archiviazione dei dati nelle infradito, nei registri e nelle unità di memoria, nonché nei sistemi che richiedono la sincronizzazione dei dati e le funzioni di mantenimento del circuito.