Guida innovativa a JK Flip-Flops: Analisi delle tabelle della verità, meccanismi e applicazioni strategiche

Questo articolo esplora l'architettura, il funzionamento e le diverse applicazioni di JK Flip-Flop, a partire dalla sua struttura di base e relazioni input-output, attraverso meccaniche operative dettagliate, alle sue implementazioni strategiche in sistemi digitali complessi.Il discorso si estende alla distinzione tra varianti innescate e innescate a livello, analizzando le rispettive utilità in ambienti sincroni e asincroni.Catalogare

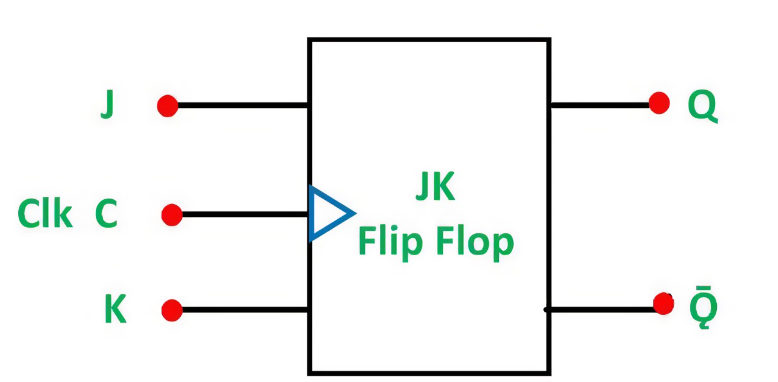

Figura 1: JK Flip-Flop

Nozioni di base di JK Flip-Flop

JK Flip-Flop è un componente di base nell'elettronica digitale, progettato per archiviare un solo bit di informazioni.Si basa sul flip-flop SR più semplice aggiungendo feedback, che aiuta a prevenire errori noti come "condizioni di gara", in cui l'output diventa instabile.

Questo flip-flop ha due input principali, J (set) e K (reset) e due uscite: Q e il suo complemento, Q '.Questi output riflettono continuamente lo stato attuale e il suo contrario, consentendo al circuito di regolare e rispondere alle modifiche di input in tempo reale.

JK Flip-Flop opera in modi specifici in base ai valori di input:

• Quando sia J che K sono 0: Il flip-flop detiene il suo stato attuale.Non si verificano cambiamenti.

• Quando sia J che K sono 1: Il flip-flop attiva il suo stato.Se Q è 0, diventa 1;Se Q è 1, passa a 0. Questa azione attivata è una caratteristica chiave che distingue il flip-flop JK da design più semplici.

• Quando J è 1 e k è 0: Il flip-flop imposta il suo stato, rendendo Q uguale a 1.

• Quando J è 0 e k è 1: Il flip-flop si ripristina, rendendo Q pari a 0.

Funzionamento del flip-flop JK

JK Flip-Flop svolge un ruolo chiave nei circuiti digitali gestendo la memoria e i tempi attraverso una risposta coordinata a segnali di input e impulsi di clock.La sua operazione dipende fortemente dai tempi degli ingressi J e K rispetto al segnale di clock, che determina come cambiano gli stati di uscita (Q e Q̅).Questa sincronizzazione garantisce che il flip-flop si comporti prevedibilmente in varie applicazioni di circuito.Il flip-flop si basa su NAND o né Gates per gestire questi cambiamenti statali.

Tenendo lo stato attuale- Quando entrambi gli ingressi J e K sono bassi (0), il flip-flop mantiene il suo stato attuale.Le porte logiche "bloccano" le uscite, garantendo che lo stato precedente (alto o basso) sia mantenuto.Questa funzione di detenzione è grave nelle applicazioni in cui i dati devono rimanere stabili fino a quando una modifica specifica è un must.

Impostazione dell'output alto (set stato) -Quando si verifica l'impulso di clock e J è alto (1) mentre K rimane basso (0), le porte logiche si regolano per impostare il flip-flop.Questo guida l'output Q a uno stato elevato (1).Ciò è utile in situazioni in cui il circuito deve attivare un output elevato, ad esempio attivando un dispositivo o memorizzando un "1" in memoria.

Cancella l'output basso (stato di ripristino) - Se J è basso (0) e K è alto (1) al momento di un impulso di clock, il flip-flop passa a uno stato di ripristino, costringendo Q a andare basso (0).Questa azione di ripristino viene spesso utilizzata nei circuiti che richiedono uno stato predefinito o cancellato dopo aver completato un'operazione, come la cancellazione dei dati dalla memoria.

Attivazione dell'output - La caratteristica unica del flip-flop emerge quando sia J che K sono alti (1).Quando arriva l'impulso di clock, il flip-flop attiva, cambiando l'uscita dal suo stato corrente a quello opposto.Se Q è alto, diventa basso e se Q è basso, diventa alto.Questa funzione di interruttore è insistente in applicazioni come contatori o dispositivi che devono alternare automaticamente tra gli stati.

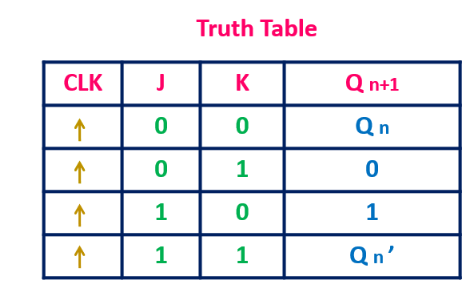

Figura 2: tabella di verità flip-flop JK

JK Flip-Flop Truth Table Analysis

La tabella della verità del flip-flop JK è uno strumento chiave per visualizzare il modo in cui reagisce a diversi segnali di input in sintonia con gli impulsi dell'orologio.Questa tabella aiuta a progettare e risolvere i circuiti digitali mostrando come le uscite del flip-flop cambiano in base a varie condizioni di input.

• Sia J che K low (J = 0, K = 0): Quando entrambi gli ingressi sono 0, il flip-flop contiene il suo stato attuale.Se Q è alto o basso, rimane invariato.Ciò è degno di nota per i circuiti in cui è desiderata una conservazione dei dati stabili, come elementi in memoria, in cui preservare lo stato attuale è adatto fino a quando non viene attivata una modifica specifica.

• J High, K basso (j = 1, k = 0): Quando J è 1 e K è 0, il flip-flop imposta l'output da Q su alto (1).Questa condizione di impostazione è utile in applicazioni che richiedono un trigger preciso per attivare un'operazione, come l'accensione di un dispositivo o l'avvio di una sequenza in un circuito logico.

• J Low, K alto (j = 0, k = 1): Con J a 0 e K a 1, il flip-flop si ripristina, rendendo Q basso (0).Questa funzione di ripristino è grave nei sistemi che devono tornare a uno stato predefinito, come quando si cancella i dati o inizializza un processo.

• Sia J che K alti (J = 1, K = 1): Quando entrambi gli ingressi sono alti, il flip-flop attiva il suo stato.Se Q è alto, diventa basso e se Q è basso, passa al massimo.Questo comportamento a legno è sostanziale per i dispositivi che devono alternare tra gli stati, ad esempio nei divisori di frequenza o sui contatori.

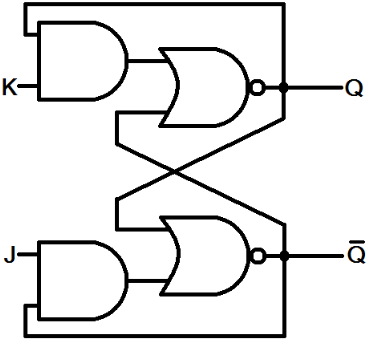

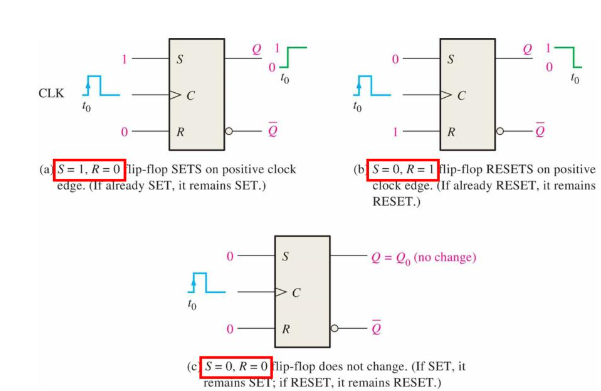

Figura 3: fermo JK

Approfondimenti sull'operazione e usi di JK Letch

Il fermo JK funziona in modo simile al flip-flop JK ma senza la necessità di un segnale di clock.Invece di aspettare un bordo dell'orologio, il fermo JK risponde continuamente per inserire i cambiamenti, rendendolo "sensibile al livello".Ciò significa che fintanto che gli input (J e K) sono stabili, l'output cambierà in tempo reale, offrendo un feedback immediato in base alle condizioni di input.

A differenza del flip-flop JK innescato dal bordo, che aggiorna la sua uscita solo quando il segnale di clock cambia (da basso a quello alto o viceversa), il latch JK regola l'uscita istantaneamente mentre gli ingressi spostano.Questa costante reattività in tempo reale è preziosa negli scenari in cui si desidera un'azione immediata senza il ritardo causato dalla sincronizzazione dell'orologio.

Filtri del rumore: Nei circuiti digitali che devono filtrare rapidamente il rumore indesiderato, la reazione istantanea del latch JK alle variazioni di input è influente.Poiché non attende un impulso di clock, può regolare l'uscita non appena viene rilevato il rumore, impedendo i ritardi nella correzione del segnale.

Elementi di memoria semplici: Il fermo JK può fungere da unità di memoria di base nei sistemi che non richiedono un controllo complesso e clock.Poiché il chiavistello mantiene l'uscita stabile fintanto che gli ingressi non cambiano, contiene efficacemente lo stato corrente, il che è utile per i circuiti che devono conservare le informazioni senza il sovraccarico delle operazioni crollate.

Figura 4: Analisi del diagramma di temporizzazione per il flip-flop JK

Analisi del diagramma di temporizzazione di JK Flip-Flops

Un diagramma di temporizzazione di JK Flip-Flop fornisce una rottura visiva di come l'uscita risponde a diversi input, sincronizzato con le transizioni degli impulsi dell'orologio.Questo diagramma mostra la relazione tra il segnale dell'orologio (CLK) e gli input (J e K) e il modo in cui influenzano collettivamente le uscite (Q e Q ').Aiuta a mappare il comportamento del flip-flop attraverso stati sequenziali, rendendo più facile comprenderne il funzionamento.

In primo luogo, il diagramma evidenzia che le uscite vengono aggiornate solo sui bordi in aumento o in calo dell'impulso di clock.Questa caratteristica, nota come trigger edge, è dominante per l'operazione di JK Flip-Flop.Mostra che anche se gli ingressi J e K cambiano, l'uscita rimane invariata fino a quando non si verifica il bordo dell'orologio, garantendo transizioni prevedibili e stabili.

Quindi, mentre il diagramma mappa le variazioni degli input J e K, è visivamente Dimostra come ogni combinazione di input influisce sull'output. Ad esempio, quando sia J che K sono bassi (0), l'output contiene il suo stato attuale.Quando J è alto e K è basso, l'uscita è impostata.Questa chiara rappresentazione visiva aiuta gli utenti a capire come il flip-flop reagisce a diverse combinazioni di input in tempo reale.

Finalmente, Il diagramma di temporizzazione mostra chiaramente le transizioni tra diversi stati di uscita, che si tratti di tenuta, impostazione, ripristino o attiva.Ogni cambiamento di stato è legato direttamente alle condizioni di input e al bordo dell'orologio, che mostra una relazione causa-effetto che è focalizzata per la progettazione e la risoluzione dei problemi di circuiti.

Applicazioni versatili di infradito JK

JK Flip-Flops sono componenti principali in una vasta gamma di sistemi digitali, noti per la loro flessibilità e affidabilità.La loro capacità di gestire operazioni logiche complesse li rende necessari in diverse applicazioni chiave, tra cui:

Figura 5: memoria di memoria

Le infradito JK sono comunemente usate per archiviare singoli bit di dati, rendendoli elementi fondamentali in array di memoria e registri.Ogni flip-flop detiene un bit, garantendo un'archiviazione di dati affidabile, che è utile nella progettazione di sistemi di memoria più grandi.

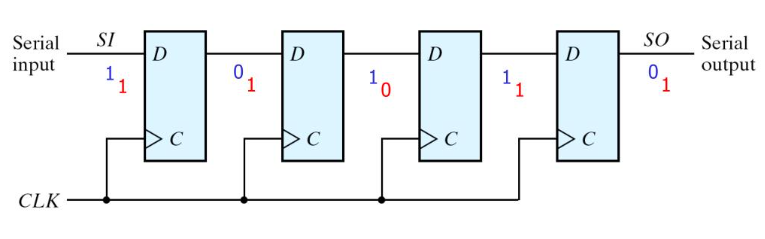

Figura 6: contatori e registri del cambio

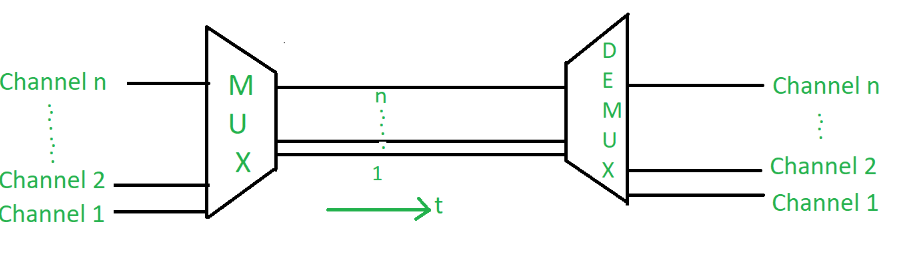

Le infradito JK sono dinamiche nelle operazioni di sequenziamento.Sono ampiamente utilizzati nei contatori per il conteggio di eventi o impulsi e nei registri a turni per la conversione dei dati seriali in formati paralleli.Ciò li rende utili nella gestione e nella manipolazione dei dati in diverse fasi di un processo, come nei sistemi di comunicazione.

Figura 7: divisione di frequenza

Nell'elaborazione del segnale, le infradito JK vengono spesso utilizzate per la divisione di frequenza.Attivando il proprio stato con ogni impulso di clock, dividono la frequenza del segnale di ingresso, creando un segnale di clock più lento e gestibile.Ciò è degno di nota in applicazioni come la gestione del segnale dell'orologio, in cui si desidera il controllo dei tempi.

Figura 8: sincronizzazione

Le infradito JK aiutano a sincronizzare più processi digitali garantendo che diverse parti di un sistema operino insieme in modo coordinato.Garantiscono che vari componenti rispondano correttamente ai segnali a tempo, mantenendo in sintonia l'intero sistema.

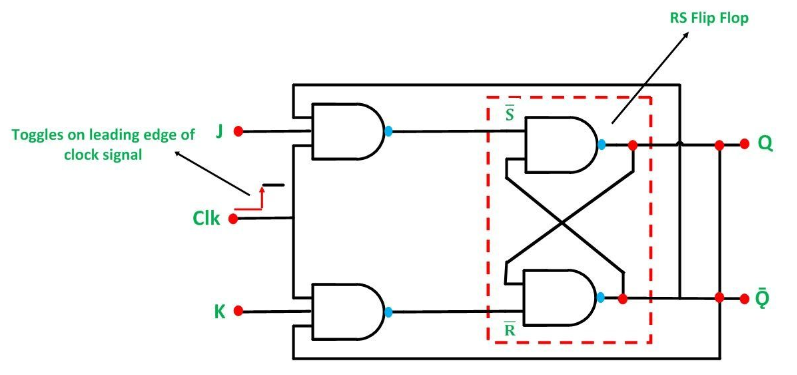

Figura 9: JK Flip-Flop: innescato e innescato a livello

Diversi tipi di infradito JK

Le infradito JK sono disponibili in due tipi principali: innescati e innescati a livello, ciascuno progettato per requisiti operativi diversi.

Flip-flop JK innescato a Edge: Cambia il loro stato solo in punti specifici, quando il segnale dell'orologio passa da basso a alto (bordo di salita) o alto a basso (bordo di caduta).Questa caratteristica li rende ideali per i sistemi in cui è insistente un tempismo preciso.Poiché i cambiamenti di stato si verificano esattamente sul bordo dell'orologio, questi infradito assicurano che tutti gli aggiornamenti avvengano in sincronizzazione con l'impulso di clock.Questo comportamento prevedibile è dinamico in ambienti strettamente controllati come orologi digitali, registri e circuiti più sequenziali.Qui, i tempi di ogni cambiamento sono gravi per mantenere la stabilità del sistema e garantire che le operazioni siano sincronizzate.

Flip-flop JK innescato a livello: Azionare diversamente, reagendo al segnale di ingresso fintanto che il segnale di clock è a un livello particolare, sia alto che basso.Non aspettano una transizione specifica dell'orologio.Invece, fintanto che l'input soddisfa le condizioni richieste, il flip-flop cambierà gli stati.Questo comportamento rende le infradito innescate di livello più adatte ai sistemi asincroni, in cui gli input potrebbero non allinearsi con un normale impulso di clock.Forniscono flessibilità nei sistemi in cui gli input sono imprevedibili o arrivano a intervalli irregolari, ad esempio in determinate attività di elaborazione del segnale o sistemi di monitoraggio che devono reagire immediatamente al cambiamento degli input.

Pro e contro di JK Flip-Flop

JK Flip-Flops offre diversi vantaggi ma sono anche forniti con alcuni compromessi che devono essere attentamente pesati durante la progettazione di sistemi digitali.

|

Professionisti |

|

|

Versatilità |

Le infradito JK sono altamente flessibili e possono

essere utilizzato in vari circuiti digitali come memoria di memoria, contatori e

sistemi di controllo.Possono attivare, impostare o ripristinare in base a diversi input

condizioni, rendendole adatte a una vasta gamma di applicazioni che

richiedono un controllo preciso sulle transizioni statali. |

|

Meccanismo di auto-correzione |

Una delle caratteristiche straordinarie di JK

Flip-Flops è il loro circuito di feedback integrato, che aiuta a correggere logico

stati dinamicamente.Questa auto-correzione garantisce che il circuito rimanga

stabile durante il funzionamento, anche quando gli ingressi cambiano rapidamente. |

|

Mitigazione delle condizioni di gara |

A differenza delle infradito più semplici, JK Flip-Flops

sono progettati per prevenire le condizioni della gara: siti in cui diventa l'output

instabile a causa di segnali di input contrastanti.Questa capacità di mantenere

L'output costante, anche in cambi di input rapidi e sequenziali, migliora il

affidabilità del circuito. |

|

Contro |

|

|

Design complesso |

Le infradito JK sono più complicate di

Flip-flop di base.Il loro design richiede ulteriori cancelli logici e input

monitoraggio, che può rendere il circuito più difficile da progettare e

Risoluzione dei problemi, specialmente nei sistemi in cui è preferita la semplicità. |

|

Ritardo di propagazione |

Il gate interno utilizzato per gestire lo stato

Le transizioni introducono un ritardo nella rapida elaborazione dei segnali.In

Applicazioni ad alta velocità, questo ritardo può influire sui tempi complessivi e rallenta

le prestazioni del circuito. |

|

Più consumo di energia |

A causa della loro complessità e della necessità di farlo

Monitorare costantemente le condizioni di input, le infradito JK consumano più potenza

Rispetto alle infradito più semplici.In sistemi più grandi o sensibili alla potenza

Applicazioni, questa maggiore domanda di potere può diventare uno svantaggio |

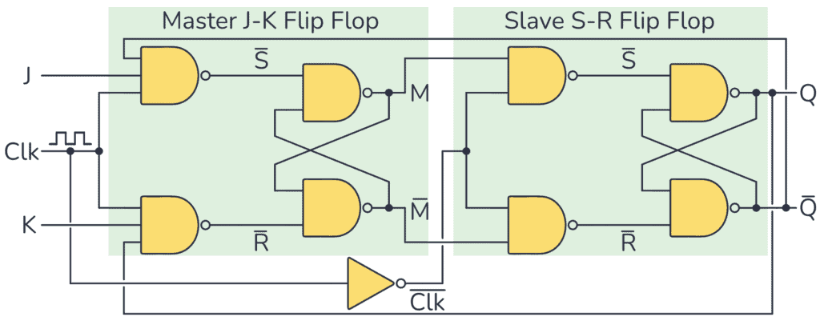

Figura 10: Flip-flop JK Master-Slave

Decodifica il flip-flop JK Master-Slave

Il flip-flop JK Master-Slave è progettato per risolvere le condizioni di gara che si trovano nelle flip-flop JK standard utilizzando un processo in due fasi per gestire input e output in modo più efficiente.

Il primo stadio, chiamato stadio principale, cattura i valori di input quando il segnale di clock raggiunge un vantaggio specifico, aumentando o caduta.A questo punto, i dati di input sono bloccati, il che significa che ulteriori modifiche agli input non influiscono sullo stato acquisito fino al ciclo di clock successivo.Questa fase garantisce che il flip-flop registri l'input corretto senza essere influenzato da eventuali cambiamenti successivi durante lo stesso ciclo di clock.

Dopo il completamento della fase principale, il palcoscenico degli slave entra in gioco.Questa fase aggiorna l'output in base ai dati acquisiti dalla fase principale, ma solo al bordo dell'orologio successivo.Separando l'acquisizione di input dall'aggiornamento dell'output, lo stadio degli slave garantisce che l'output rimanga stabile fino a quando la fase principale non abbia elaborato completamente l'input.Ciò impedisce eventuali modifiche premature o non intenzionali nell'output durante il ciclo di clock.

Perché la configurazione Master-Slave è importante?

Il processo a due stadi stabilizza il funzionamento del flip-flop JK, prevenendo oscillazioni indesiderate o fluttuazioni che possono avvenire in configurazioni più semplici, specialmente quando entrambi gli ingressi sono mantenuti.Dicottando l'elaborazione di input dalla modifica dell'output, la configurazione di Master-Slave garantisce che gli output rimangano prevedibili e stabili, anche in situazioni in cui i tempi sono preziosi.

Affrontare la gara in termini di condizione in Flip-flops JK

Le condizioni di razza si verificano nelle infradito JK quando entrambi gli input, J e K, sono alti e il segnale di clock rimane attivo per troppo tempo.Ciò porta a un continuo attivazione delle uscite, che possono causare comportamenti irregolari e interrompere l'affidabilità del circuito.

La configurazione di Master-Slave utilizza un processo a due stadi per prevenire problemi di gara.Lo stadio principale cattura i valori di input sul bordo dell'orologio e li blocca. La fase di slave aggiorna le uscite al bordo dell'orologio successivo, garantendo che l'uscita non cambi fino a quando gli ingressi non vengono elaborati completamente.Questo approccio impedisce effettivamente l'uscita di attivare in modo incontrollabile, anche se gli input rimangono elevati per un periodo prolungato.

Un altro metodo per evitare le condizioni di razza è regolare la durata dell'impulso di clock.Rendendo il polso dell'orologio più corto del ritardo di propagazione del flip-flop, è possibile garantire che lo stato non cambi più di una volta all'interno dello stesso ciclo di clock.Ciò impedisce al flip-flop di attivare ripetutamente durante un singolo ciclo, stabilizzando l'uscita.

Dinamica del cambio di flip-flop JK

Il comportamento di commutazione di un flip-flop JK è in gran parte guidato dai tempi del segnale di clock e dai livelli di ingresso (J e K).Lo stato di flip-flop cambia in base agli ingressi presenti sul bordo positivo del segnale di clock.In questo momento pericoloso, il flip-flop valuta gli input e aggiorna il suo output di conseguenza.

Quando il segnale di clock colpisce il bordo di salita, il flip-flop JK legge gli stati attuali degli ingressi J e K.A seconda dei loro valori, il flip-flop manterrà, imposterà, ripristinerà o attiverà la sua uscita.

Orologi digitali: La precisione è tutto negli orologi digitali e le infradito JK aiutano a mantenere questa precisione assicurando che i cambiamenti di stato si verifichino solo a intervalli di clock precisi.

Tester logici sequenziali: Nei sistemi che testano la funzionalità dei circuiti logici, le infradito JK svolgono un ruolo nel verificare che ciascun componente risponda correttamente a segnali a tempo specifici.

Altri sistemi sensibili al tempo: In varie applicazioni digitali in cui i tempi sono rischiosi, come sistemi di comunicazione o unità di elaborazione dei dati, il flip-flop JK garantisce che le transizioni di stato si verifichino in sincronia con l'orologio, prevenendo errori di temporizzazione.

Conclusione

Il flip-flop JK si distingue come un elemento finale nella progettazione del circuito digitale, che offre una miscela di versatilità e precisione alla disperata ricerca di una vasta gamma di applicazioni che vanno dalla memoria di memoria alla divisione di frequenza e alla sincronizzazione dei processi digitali.La sua capacità di mitigare le condizioni di razza attraverso configurazioni innovative come la disposizione di Master-Slave sottolinea la sua adattabilità nel risolvere sfide di progettazione intrinseche.Allo stesso modo, il grave ruolo del flip-flop nel garantire transizioni statali precise evidenzia la sua natura necessaria nella creazione e nella manutenzione di sistemi digitali affidabili ed efficienti.Con l'avanzare della tecnologia, i progetti e le applicazioni in evoluzione del flip-flop JK continuano a essere fondamentali per spingere i confini dell'elettronica digitale verso architetture più sofisticate e robuste.

Domande frequenti [FAQ]

1. Quali sono le applicazioni di JK Flip Flop?

Il flip-flop JK è ampiamente utilizzato nell'elettronica digitale per una varietà di attività:

Applicazioni di temporizzazione: Può servire come elemento di ritardo o un timer quando è collegato in determinate configurazioni.

Contatori e registri: Attivando il proprio stato con ogni impulso di clock, viene utilizzato nella progettazione di vari contatori e spostamenti che sono definitivi nei circuiti logici sequenziali.

Memoria di memoria: Fornisce un'unità di base di memoria di memoria, utile per archiviare bit in applicazioni computazionali.

2. In che modo un flip-flop JK funziona con una tabella della verità?

Un flip-flop JK ha due ingressi (J e K) e un segnale di clock.La sua operazione varia in base agli stati di input, sincronizzati all'orologio:

• J = 0, k = 0: l'output non cambia.

• J = 0, k = 1: l'output si ripristina a 0.

• J = 1, k = 0: l'output è impostato su 1.

• J = 1, K = 1: l'uscita attivo (ovvero se era 0, diventa 1 e viceversa).

3. Che cos'è JK Flip Flop e funziona?

Un flip-flop JK combina le proprietà dei flip-flop SR e T.Evita la condizione "proibita" osservata nelle infradito SR usando gli input JK in modo efficace:

Lo stato del flip-flop è controllato dagli ingressi J e K, che determinano se l'uscita deve contenere, ripristinare, impostare o attivare, in sintonia con il bordo di salita o di caduta dell'impulso di clock.

4. Quali sono le applicazioni di chiusura e infradito?

Archiviazione dei dati: I chiavistei e le infradito sono gravi per l'archiviazione dei dati all'interno di registri e array di memoria.

Divisione di frequenza: Utilizzato nei divisori di frequenza a causa della loro capacità di cambiare gli stati sui bordi dell'orologio, dimezzando la frequenza con ogni fase di una serie.

Macchine a stato: Basic nella progettazione di macchine a stato finito che vengono utilizzate per implementare i circuiti sequenziali di logica e controllo.

Debouncing: Utilizzato per stabilizzare i segnali da interruttori meccanici e pulsanti, garantendo transizioni singole e pulite.

5. A cosa servono le infradito?

Storage binario: Ogni flip-flop memorizza un po 'di dati, rendendoli blocchi per dispositivi di archiviazione binaria.

Dividi dell'orologio: Dividono la frequenza dell'orologio di input per due, utile negli orologi digitali e nelle applicazioni di temporizzazione.